1. Overview

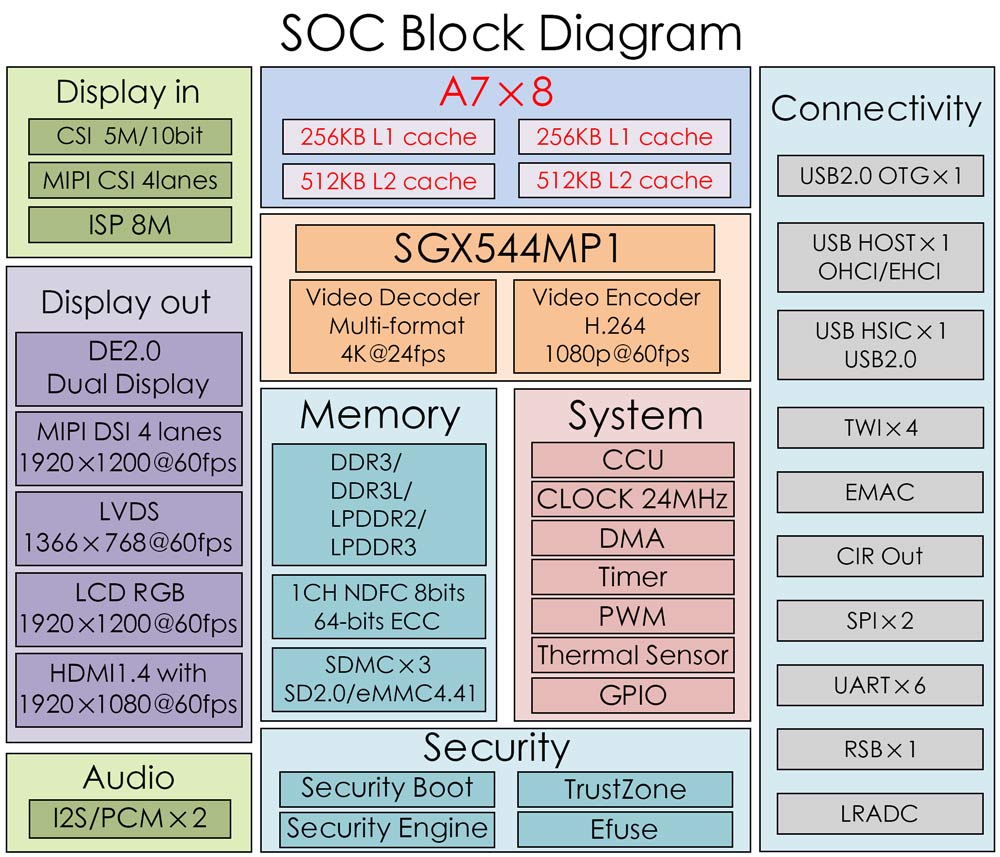

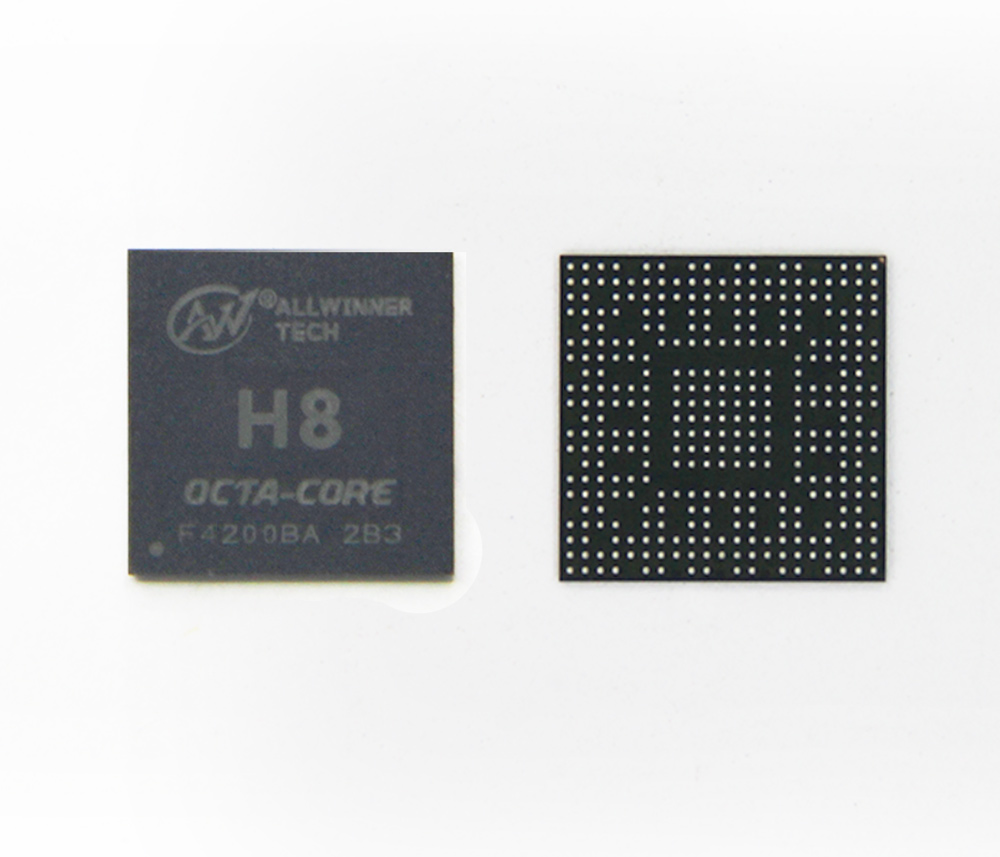

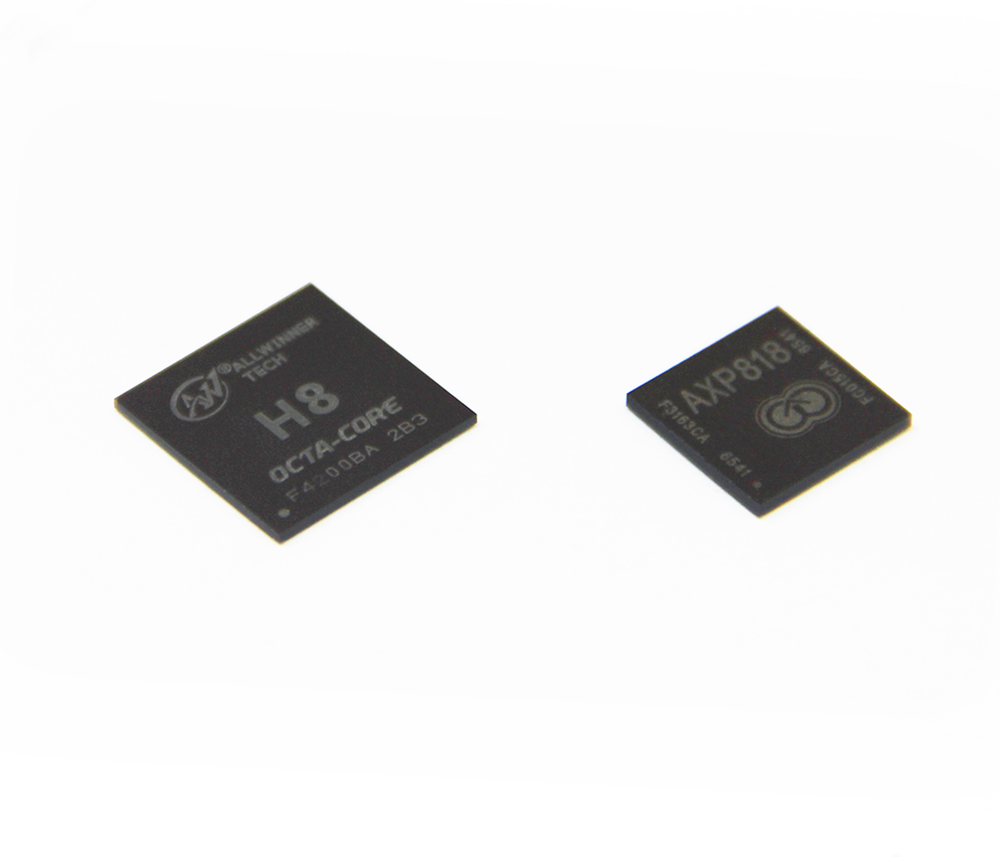

The Allwinner’s H8 is a remarkably lower power, high performance octa-core home entertainment processor based on ARM Cortex TM -A7 CPU along with SGX544MP1 GPU architecture. It is also highly competitive in term of system cost thanks to its high system integration and is capable of delivering excellent user experience while maintaining low power consumption.

Main features of H8 include:

● CPU architecture: Based on an octa-core Cortex TM -A7 CPU architecture, the most power efficient CPU core ARM’s ever developed.

● Graphics: H8 adopts the extensively implemented and technically mature PowerVR SGX544MP1 to provide mobile users with superior experience in web browsing, video playback and games; OpenGL ES1.1/2.0, OpenCL1.1 and DirectX 9.3 standards are supported.

● Video Engine: Multi-format playback of up to 4K high-definition video, and support MPEG1/2, MPEG4 SP/ASP GMC, H.263 including Sorenson Spark, H.264 BP/MP/HP, VP8, WMV9/VC1, JPEG/MJPEG standards with dedicated hardware, and HEVC/H.265 decoder 1080p@30fps with software.

● Display: Supports RGB/LVDS/DSI/HDMI interface to 1920×1200 resolution. Four-lane MIPI DSI is integrated as well.

● Memory Controller: Support external memory interfaces to NAND Flash,SD/eMMC,Nor Flash and SDRAM port. SDRAM port can be configured to support LPDDR2,LPDDR3,DDR3,DDR3L.

● HawkView TM ISP: Support camera up to 8MPixels@30fps,better spatial de-noise and chrominance de-noise, Zone-based AE/AF/AWB statistics, Programmable color correction, Anti-flick detection statistics.

To reduce total system cost and enhance overall functionality,H8 has a broad range of hardware peripherals such as MIPI CSI,LCD controller, Power management, DMA, Timers, High Speed Timer, Security System, GPIO, Digital Audio,UART,SPI,CIR,USB2.0,TWI etc.

2. Feature

2.1. CPU Architecture

● ARMv7 ISA standard instruction set plus Thumb-2 and Jazeller RCT

● NEON with SIMD and VFPv4

● Support LPAE

● 32KB I-cache and 32KB D-cache per CPU

● 1MB L2-cache

2.2. GPU Architecture

● PowerVR SGX544MP1

● Support OpenGL ES 1.1/2.0

● Support OpenCL 1.1

● Support Directx 9.3 standards

● Support RenderScript

2.3. Memory Subsystem

Boot ROM

● Size:96KB

● Support secure and non-secure boot

● Support system boot from Raw NAND, eMMC, SD/TF card and SPI Nor Flash

● Support system code download through USB OTG

SDRAM

● Compatible with JEDEC standard LPDDR2/LPDDR3/DDR3/DDR3L SDRAM

● Up to 2GB address space

● 16 address signal lines and 3 bank signal lines

● 32-bit bus width

● Support Memory Dynamic Frequency Scale

NAND Flash

● Up to 4 flash chips

● 8-bit data BUS width

● 64-bit ECC per 1024 bytes

● Support 1024,2048,4096,8192,16K bytes size per page

● Support SDR,ONFI DDR and Toggle DDR NAND

SD/MMC Interface

● Up to three SD/MMC controllers

● 1/4/8-bit SD,SDIO,MMC mode

● Compatible with eMMC standard specification V4.41, SD physical layer specification V2.0, SDIO card specification V2.0

● Data rate up to 100Mbps

● Support SDIO suspend and resume operation

● Support hardware CRC generation and error detection

● Support SDIO interrupt detection

● Support block size from 1 to 65535 bytes

2.4. System Peripheral

Timer

● Two on-chip timers with interrupt-based operation

● 33-bit Audio/Video Sync Counter

● One watchdog to generate reset signal or interrupts

● 24MHz or Internal OSC clock input

High Speed Timer

● Counters up to 56bits

● Clock source is synchronized with AHB clock, much more accurate than other timers

OSC24M

● Support 1.8v oscillator

● Support internal RC oscillator

GIC

● Support 16 SGIs(Software Generated Interrupt), 16 PPIs(Private Peripheral Interrupt) and 168 SPIs(Shared Peripheral Interrupts)

DMA

● 8-channel DMA

● Flexible data width of 8/16/32 bits

● Support linear and IO address modes

● Support data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

CCU

● 11 PLLs

● Support a 24MHz oscillator and an on-chip RC oscillator

● Clock configuration for corresponding modules

● Support software-controlled clock gating and software-controlled reset for corresponding modules

PWM

● Up to two PWM channels

● Support outputting two kinds of waveform: continuous waveform and pulse waveform

● 0% to 100% adjustable duty cycle

● Up to 24MHz output frequency

Security System

● Support symmetrical algorithm: AES, DES, TDES

● Support asymmetrical algorithm:RSA512/1024/2048/3072-bits

● Support hash algorithm:SHA-1/SHA-224/SHA-256, MD5

● 160-bits hardware PRNG with 192-bits seed

● 256-bits TRNG

● 32-bits hardware CRC

● Support ECB,CBC,CTR modes for DES/TDES

● Support ECB, CBC, CTR,CTS modes for AES

● 128-bits, 192-bits and 256-bits key size for AES

Security ID

● Support 2k-bits EFUSE for chip ID and security application

TrustZone

● Support TrustZone technology

● Support 96KB security SRAM

CPU Configuration

● Support power clamp

● Flexible CPU configuration

Power Management

● Support DVFS for CPU frequency and voltage adjustment

● Flexible clock gate and module reset

● Support dynamic frequency adjustment for external DRAM

● Support multiple power domains

2.5. Display Subsystem

Display Engine2.0

● Input layer size up to 2048×2048, and output size up to 2048×2048

● Support four alpha blending channel for main display, two channel for aux display

● Support four overlay layers in each channel, and has a independent scaler

● Support potter-duff compatible blending operation

● Support input format YUV422/YUV420/YUV411/ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555 and RGB565

● Support Frame Packing/Top-and-Bottom/Side-by-Side Full/Side-by-Side Half 3D format data

● Support display enhancement 2.0 for excellent display experience

– Adaptive edge sharping

– Adaptive color enhancement

– Adaptive contrast enhancement and fresh tone rectify

● Support write back & rotation for high efficient dual display and miracast

Video Output

● Support two independent display channels

● Support RGB(24bits) up to 1920×1200@60Hz resolution

● Support RGB666/656 ditcher function

● Support LVDS up to 1366×768@60Hz resolution

● Support 4-lane MIPI DSI(V1.0) up to 1920×1200@60Hz resolution

● Support HDMI V1.4 output with HDCP1.2 up to 1920×1080@60Hz resolution

2.6. Video Engine

Video Decoding

● Support multi-format video decoder, including:

– MPEG1 MP/HL up to 1080p@60fps

– MPEG2 MP/HL up to 1080p@60fps

– MPEG4 SP/ASP up to 1080p@60fps

– H.263 BP up to 1080p@60fps

– H.264 BP/MP/HP up to 4K@24fps or 1080p@60fps

– VP8 up to 1080p@60fps

– VC1 SP/MP/AP up to 1080p@30fps

– JPEG/MJPEG up to 1080p@30fps

● Support HEVC/H.265 decoder(software),Main Profile,1080p@30fps

Video Encoding

● Support H.264 video encoding up to 1080p@60fps,720p@120fps

● JPEG baseline: picture size up to 8192×8192

● Support input picture size up to 4800×4800

● Support input format: tiled(128×32)/YU12/YV12/NU12/NV12/ARGB/YUYV

● Support Alpha blending

● Support thumb generation

● Support 4×2 scaling ratio: from 1/16 to 64 arbitrary non-integer ratio

● Support rotated input

2.7. Image Subsystem

CSI

● Support 10-bits parallel camera sensor

● Support up to 5M pixel camera sensor

● Support video shot up to 720p@30fps

MIPI CSI

● 4-lane MIPI CSI

● Support up to 8M pixel camera sensor

● Support video shot up to 1080p@60fps

ISP

● Support input formats:8/10-bits RAW RGB,8-bits YCbCr

● Support output formats: YCbCr420 semi-planar,YCrCb420 semi-planar, YCbCr422 semi-planar,YCrCb422 semi-planar,YUV420 planar,YUV422 Planar

● Support image mirror flip and rotation

● Support two output channels

● Speed up to 8MPixels@30fps

● Defect pixel correction

● Super lens shading correction

● Anisotropic non-linear Bayer interpolation with false color suppression

● Programmable color correction

● Advanced contrast enhance and sharping

● Advanced saturation adjust

● Advanced spatial(2D) de-noise filter

● Advanced chrominance noise reduction

● Zone-based AE/AF/AWB statistics

● Anti-flick detection statistics

● Histogram statistics

2.8. External Peripherals

USB

● USB 2.0 OTG

– Complies with USB2.0 Specification

– Support High-Speed(HS,480Mbps),Full-Speed (FS,12Mbps),and Low-Speed (LS,1.5Mbps) in Host mode

– Up to 10 User-Configurable Endpoints

– Support point-to-point and point-to-multipoint transfer in both Host and Peripheral mode

● Two EHCI/OHCI compliant Host SIE multiplexed with one USB 2.0 analog PHY, one HSIC PHY

– Support High-Speed (HS,480Mbps),Full-Speed (FS,12Mbps),and Low-Speed(LS,1.5Mbps) Device

– An internal DMA Controller for data transfer with memory

EMAC

● Support 10/100/1000Mbps data transfer rate

● Support MII/RGMII PHY interface

● Support full-duplex and half-duplex operation

● Programmable frame length

● Flexible address filtering modes

● Automatic CRC and pad generation controllable on a per-frame basis

● Options for Automatic Pad/CRC Stripping on receive frames

● Programmable frame length to support Standard or Jumbo Ethernet frames with sizes up to 16 KB

● Programmable Inter Frame Gap (40-96 bit times in steps of 8)

● Supports a variety of flexible address filtering modes

LRADC

● LRADC with 6-bit resolution

● Support hold key and continuous key

● Support single key, normal key and continuous key

Digital Audio

● PCM/I2S

– I2S and PCM are configurable through software

– Support I2S formats: normal, left-justified, right- justified

– Audio data resolution:16bits, 20bits, 24bits

– Audio sample rate up to 192KHz

– Master and slave work mode are configurable

● TDM(Time Division Multiplexing)

– Master/Slave mode

– Audio sample resolution from 8bits to 32bits`

– Sample rate from 8KHz to 192KHz

– 4 data output pin

– DMA-based or interrupt-based operation

● OWA(One Wire Audio)

– Support channel status insertion for the transmitter

– 32x24bits TX FIFO for audio data transfer

– Programmable FIFO thresholds

CIR

● A flexible receiver for IR remote

● Programmable FIFO thresholds

UART

● Up to six UART controllers

● 64-Bytes Transmit and receive data FIFOs for all UART

● Compliant with industry-standard 16550 UARTs

● Support Infrared Data Association(IrDA) 1.0 SIR

SPI

● Up to two SPI controllers

● Master/Slave configurable

● Mode0~3 are supported for both transmit and receive operation

● Two 64-Bytes FIFO for SPI-TX and SPI-RX operation

● DMA-based or interrupt-based operation

● Polarity and phase of the chip select(SPI_SS) and SPI_Clock(SPI_SCLK) are configurable

TWI

● Up to four TWI(Two Wire Interface) controllers

● Support Standard mode(up to 100K bps) and Fast mode(up to 400K bps)

● Master/Slave configurable

● Allows 10-bit addressing transactions

RSB TM (Reduced Serial Bus)

● A simplified two wire protocol

● Support master mode

● Support multi-slaves

● Speed up to 20Mbps

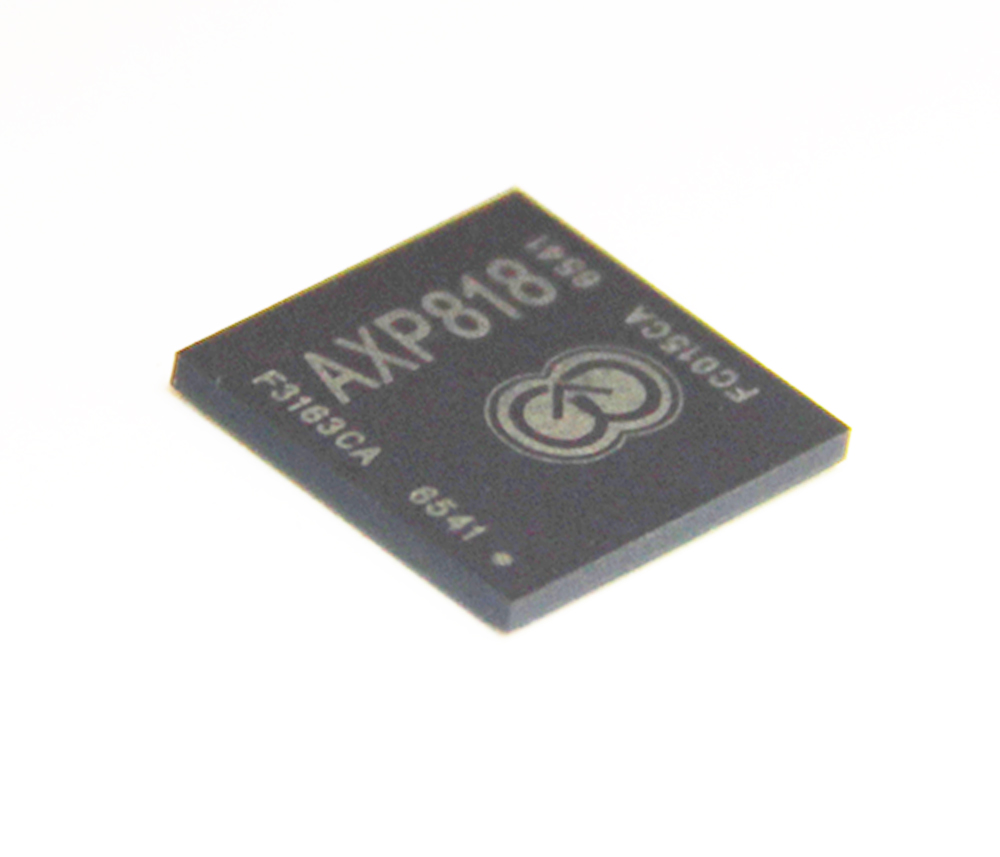

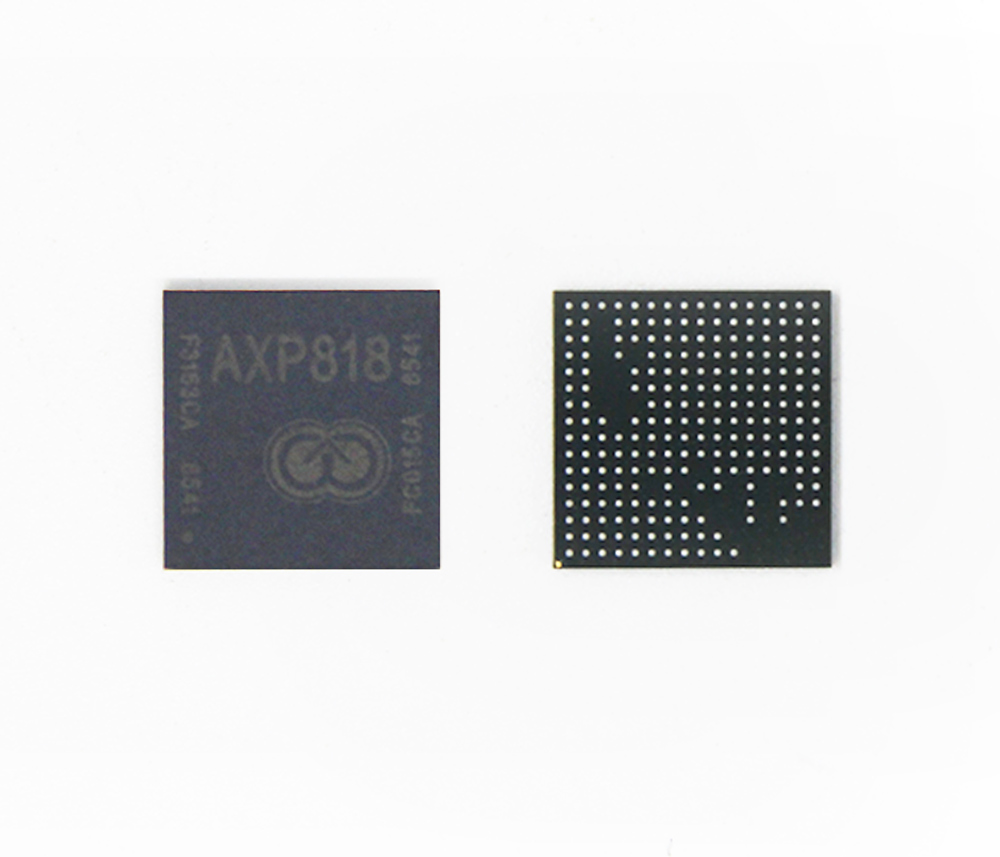

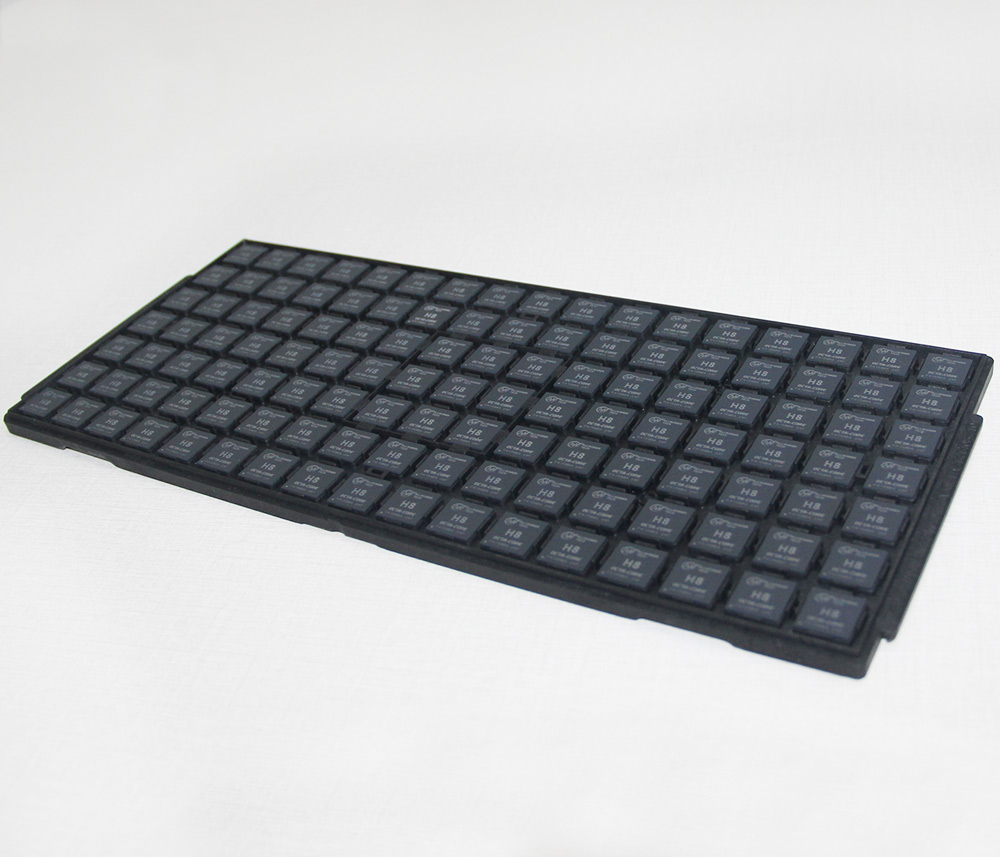

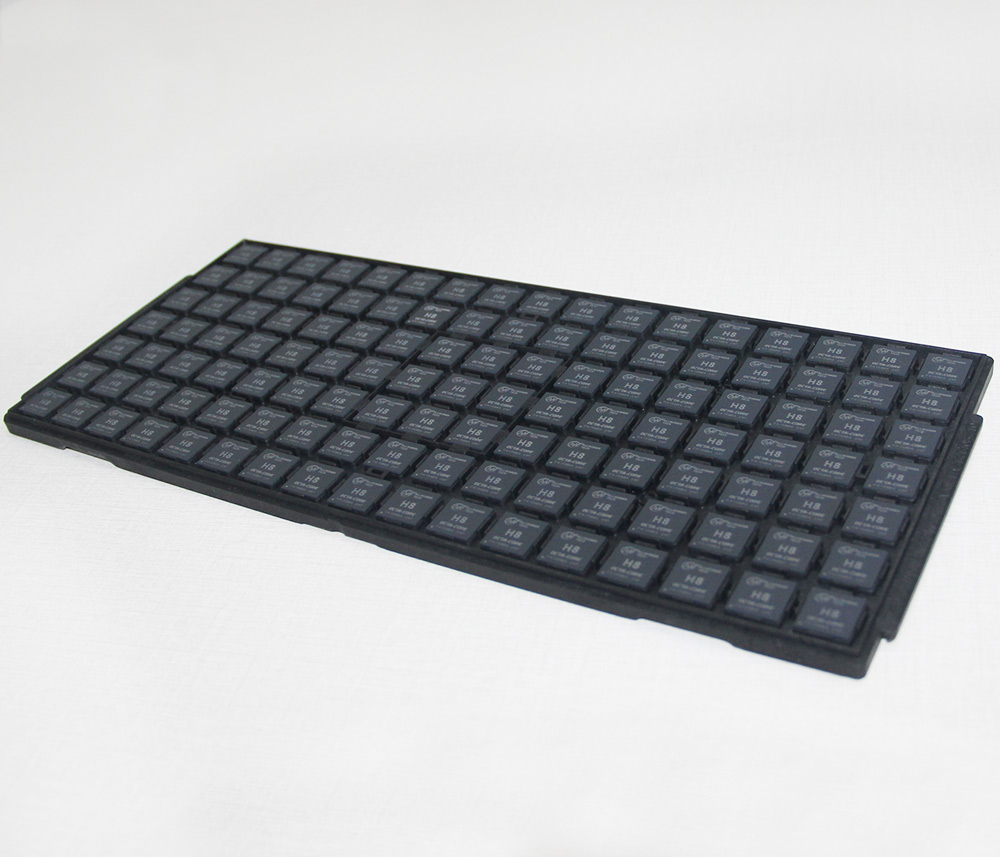

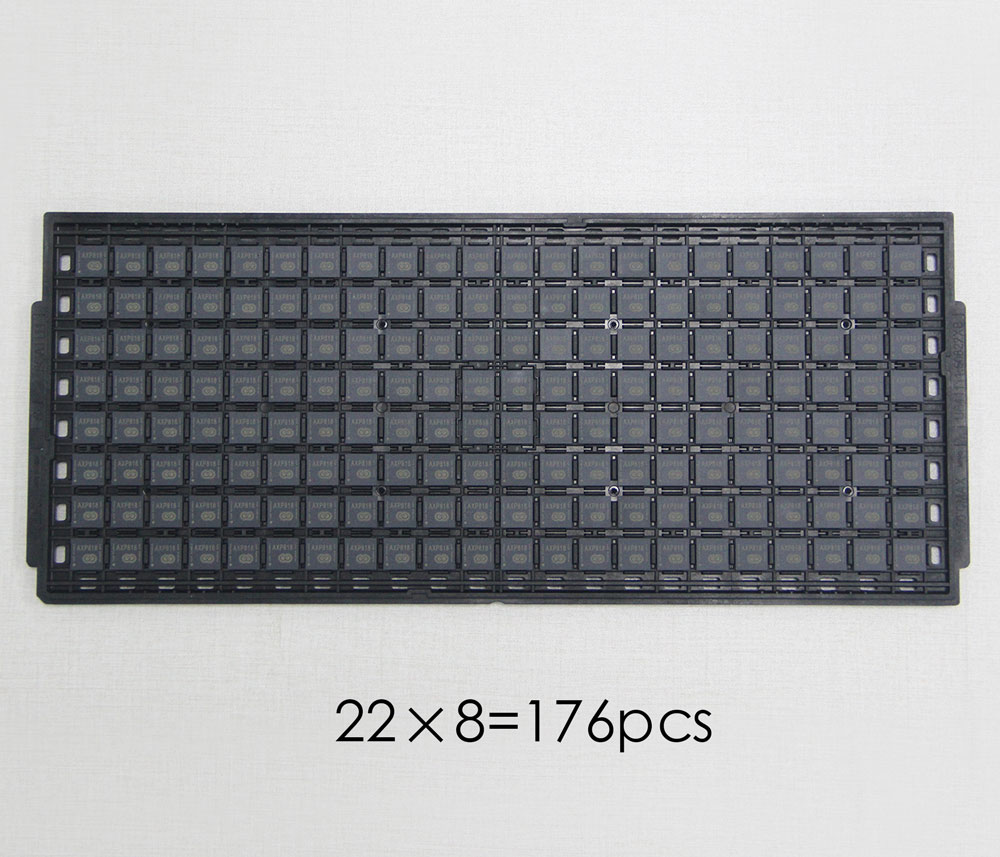

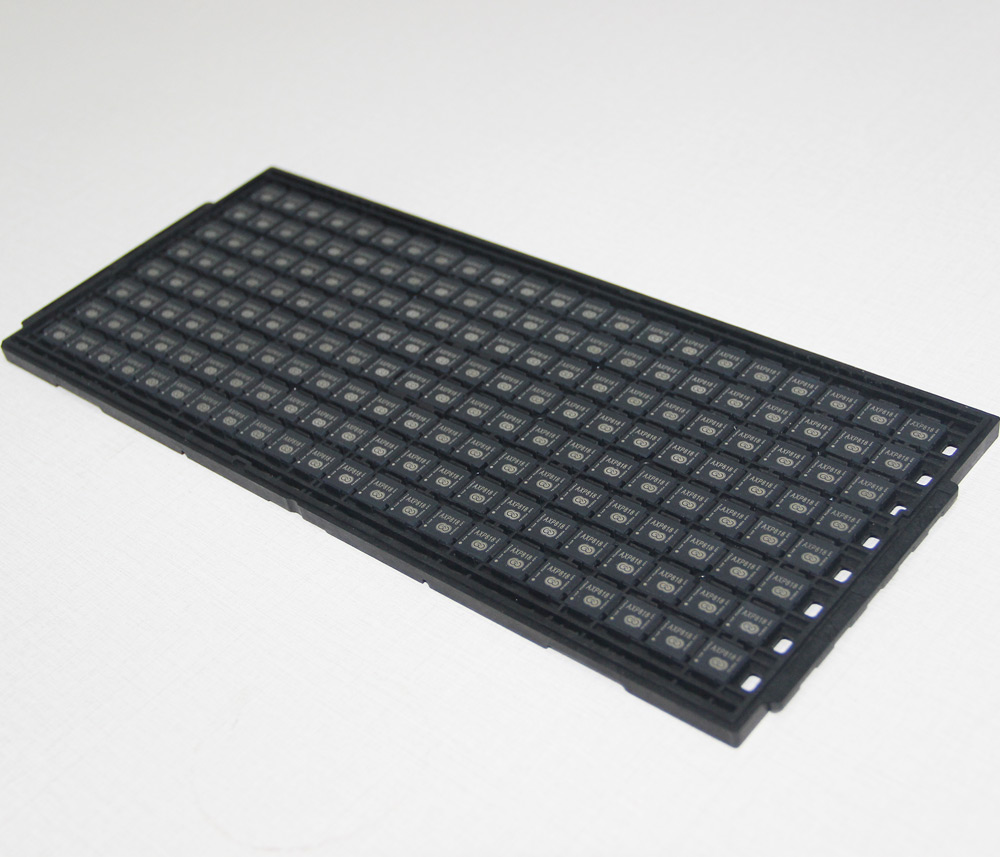

2.9. Package

● FBGA 345 balls,0.65mm ball pitch,14mm x14mm

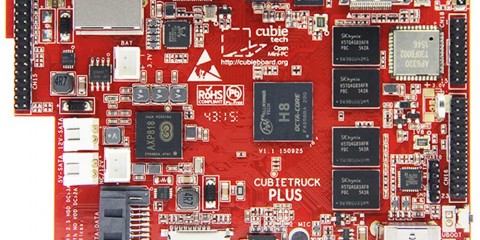

3. Development Materials

● Technical Website: http://cubieboard.org/

● Resources and Materials: http://dl.cubieboard.org/part/H8/

● DemoBoard: http://www.cubietech.com/product detail/cubieboard5/

● Distribution contacts: sales@cubietech.com

● Technical contacts: support@cubietech.com